Article

# **Voltage Support Provided by STATCOM in Unbalanced Power Systems**

Ana Rodríguez <sup>1,\*</sup>, Emilio J. Bueno <sup>2</sup>, Álvar Mayor <sup>1</sup>, Francisco J. Rodríguez <sup>2</sup> and Aurelio García-Cerrada <sup>3</sup>

- Gamesa Electric; Avda. Fuentemar, 5, Madrid, Coslada 28823, Spain; E-Mail: amayor@gamesacorp.com

- <sup>2</sup> Electronics Department, University of Alcalá, Ctra. Madrid-Barcelona, km. 33,600, Madrid, Alcalá de Henares 28871, Spain; E-Mails: emilio@depeca.uah.es (E.J.B.); fjrs@depeca.uah.es (F.J.R.)

- <sup>3</sup> Electronics and Control Department, Comillas Pontifical University; Alberto Aguilera, 25, Madrid 28015, Spain; E-Mail: aurelio@iit.upcomillas.es

- \* Author to whom correspondence should be addressed; E-Mail: anarodriguez@gamesacorp.com; Tel.: +34-91-671-0330; Fax: +34-91-671-0322.

Received: 5 December 2013; in revised form: 6 February 2014 / Accepted: 19 February 2014 / Published: 24 February 2014

**Abstract:** The presence of an unbalanced voltage at the point of common coupling (PCC) results in the appearance of a negative sequence current component that deteriorates the control performance. Static synchronous compensators (STATCOMs) are well-known to be a power application capable of carrying out the regulation of the PCC voltage in distribution lines that can suffer from grid disturbances. This article proposes a novel PCC voltage controller in synchronous reference frame to compensate an unbalanced PCC voltage by means of a STATCOM, allowing an independent control of both positive and negative voltage sequences. Several works have been proposed in this line but they were not able to compensate an unbalance in the PCC voltage. Furthermore, this controller includes aspects as antiwindup and droop control to improve the control system performance.

Keywords: PCC voltage control; STATCOM; unbalanced voltage

#### 1. Introduction

The ongoing large-scale integration of wind energy into the power system demands the continuous revision of grid codes and power quality standards in order to fulfill restrictive constraints. Furthermore, most host utilities also require that wind farms must tolerate system disturbances [1]. These requirements become of paramount importance in remote locations where the feeders are long and operated at a medium voltage level, providing a weak grid connection. The main feature of this type of connection is the increased voltage regulation sensitivity to changes in load [2]. Thus, the system's ability to regulate voltage at the point of common coupling (PCC) to the electrical system is a key factor for the successful operation of the wind farm [3], even in the face of voltage flicker caused by wind gusts or post fault electromechanical swings in the power grid [1].

Nowadays, there are grid operators that allow providing unbalanced currents so that the power at the PCC remains constant. This is very useful in weak grids because it allows connecting all loads to a balanced PCC voltage, which is especially important for sensitive loads that could disconnect if the AC voltage does not meet restrictive voltage standards.

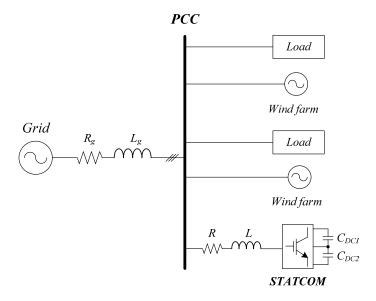

This task can be accomplished by means of a STATCOM, which is a Voltage-Source Converter (VSC) system whose prime function is to exchange reactive power with the host AC system [4] and control the power factor. In a distribution system, it is mainly used for voltage regulation [5]. This has a major application in weak grids, whose significant grid impedance may lead to large PCC voltage variations compared to that of strong grids. The general system under investigation is shown in Figure 1. Several loads and wind farms are connected to the same PCC along with a STATCOM, which is in charge of the PCC voltage regulation. In this figure, L and R are the grid filter parameters,  $L_g$  and  $R_g$  are the grid impedance parameters,  $C_{DC1}$  and  $C_{DC2}$  are the DC-link capacitors and the STATCOM is a three-level neutral point clamped (NPC) converter.

**Figure 1.** Overview of the general system under investigation.

One of the most typical disturbances in power systems is an unbalance in the PCC voltage [6], which is a difference in the magnitude of the phase-to-neutral (or phase-to-phase) voltages of a three-phase system. There is no standardized mathematical expression to quantify the unbalance of a

three-phase system. Three definitions of unbalance are reviewed in [7]; one was developed by the National Equipment Manufacturer's Association (NEMA), another was developed by the IEEE and the other is the most common definition used by engineering community (the so-called true definition). The latter expresses the voltage unbalance factor (VUF) in percent as:

$$VUF(\%) = \frac{U^{-}}{U^{+}} \cdot 100\% \tag{1}$$

where U is the root mean square (RMS) value of the negative sequence component and  $U^{\dagger}$  is the RMS value of the positive sequence component.

It is well-known that any three-phase system can be split into the sum of three balanced systems, namely, positive, negative and zero sequences. A balanced three-phase system will be only composed of a positive sequence system. However, in real power systems several types of disturbances may affect the grid and give rise to the appearance of a negative sequence system in addition to the positive sequence one. Zero sequence systems only appear in three-phase four-wire power systems [8] and this case is not tackled in this article, since a three-phase three-wire power system is considered.

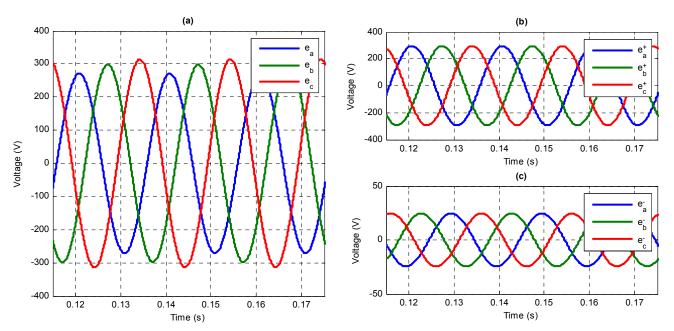

The unbalanced three-phase voltage shown in Figure 2a has a VUF equal to 8.3%, and it has been considered as the ideal grid voltage in the simulations results of Section 6.1. It is composed of the sum of a positive sequence three-phase system with  $U^+ = 0.9 \cdot 400/\sqrt{3} \approx 207.8 \text{ V}$  (Figure 2b) and a negative sequence three-phase system with  $U^- = 0.075 \cdot 400/\sqrt{3} \approx 17.3 \text{ V}$  (Figure 2c). In accordance with IEC 61000-3-13, the maximum VUF during normal operation in transmission systems must not exceed 2%; therefore, the grid voltage of Figure 2a can be used to justify and test the proposed algorithm.

**Figure 2.** (a) Unbalanced ideal grid voltage in *abc*-axes, which is composed by the sum of a (b) positive sequence three-phase system and a (c) negative sequence three-phase system.

An unbalanced voltage has several negative effects. For instance, it reduces efficiency and can cause failure in induction machines [9]. It also produces negative effects on power electronic converters. The voltage unbalance can impair a Pulse-Width Modulation (PWM) converter system

because the input active and reactive power ripples are generated by the cross products of line currents and unbalanced voltages [10]. The grid synchronization algorithm has to be sufficiently fast and accurate to extract the positive and negative voltage sequences precisely, in order to generate the output current references. A PCC voltage controller is needed to cancel these harmful effects while allowing an independent control of positive and negative sequence components.

The article is organized as follows: Section 2 analyzes the PCC voltage equations under unbalanced conditions and provides their corresponding plant models, which are focused in the grid model under a voltage unbalance. Section 3 details the control scheme that has been developed, as well as the design and tuning of the proposed PCC voltage controller. Section 4 addresses the possibility of performing an online adaptation of the DC-link reference voltage to always ensure an optimal modulation index. Section 5 investigates the sampling mode of the PCC voltage when working with an L-filter, which is of paramount importance for the correct operation of the control system in weak grids. Section 6 shows the effectiveness of the novel PCC voltage control through simulation results and, lastly, conclusions are presented in Section 7.

#### 2. Grid Modeling Under Unbalanced Conditions

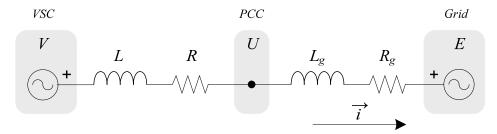

A VSC can be represented as an ideal AC voltage source (per phase). Therefore, its connection to the grid can be depicted according to the scheme of Figure 3, where L and R are the grid filter parameters,  $L_g$  and  $R_g$  are the grid impedance parameters, V is the VSC output voltage, U is the PCC voltage, E is the ideal grid voltage and  $\vec{i}$  is the current flowing from the VSC to the grid.

**Figure 3.** Unifilar diagram of the connection of the VSC to the grid through an L-filter.

In order to obtain a general model of the grid, valid for both balanced and unbalanced conditions, the scheme of Figure 3 is considered. The grid model is calculated from the voltage equation between the points U (PCC) and E (ideal grid). The grid filter is not taken into account to obtain such model, since PCC voltage variations in an unbalanced system are imposed by the grid impedance and not by the grid filter.

The grid model can be expressed in time domain and in synchronous reference frame (dq-axes) as shown in Equation (2a) for positive sequence (superscript "+") and Equation (2b) for negative sequence (superscript "-"). In these equations,  $\omega_1$  is the fundamental angular frequency  $\omega_1 = 2\pi 50$  rad/s. Each PCC voltage component is formed by the voltage drop across the grid impedance, a cross-coupling term between axes and the ideal grid voltage:

$$\vec{u}^{+}(t) = R_g \vec{i}^{+}(t) + L_g \frac{d\vec{i}^{+}(t)}{dt} + j\omega_1 L_g \vec{i}^{+}(t) + \vec{e}^{+}(t)$$

(2a)

$$\vec{u}^{-}(t) = R_g \vec{t}^{-}(t) + L_g \frac{d\vec{t}^{-}(t)}{dt} - j\omega_1 L_g \vec{t}^{-}(t) + \vec{e}^{-}(t)$$

(2b)

Each of these voltages is separated into its d and q projections: positive sequence voltages  $u_d^+$  and  $u_q^+$  are shown in Equation (3a) and (3b), whereas negative sequence voltages  $u_d^-$  and  $u_q^-$  are shown in Equation (4a) and (4b). These four expressions are steady-state approximations. Grid resistance  $R_g$  is considered to be very small, so that its contribution to the PCC voltage can be neglected (compared to the voltage drop across the grid filter inductance). Furthermore, the derivative of a constant signal (such as  $\vec{t}$  in dq-axes) is zero. Note that  $u_d^+$  is equal to zero Equation (3a) because a Phase-Locked Loop (PLL) is used to synchronize the positive sequence PCC voltage vector  $(\vec{u}^+)$  with the q-axis, hence the projection of  $\vec{u}^+$  on this axis is equal to its amplitude  $(u_q^+ \equiv |\vec{u}^+|)$ :

$$u_d^+ = 0 (3a)$$

$$u_q^+ \approx \omega_1 L_g i_d^+ + e_q^+ \tag{3b}$$

$$u_d^- \approx \omega_1 L_g i_q^- + e_d^- \tag{4a}$$

$$u_q^- \approx -\omega_1 L_g i_d^- + e_q^- \tag{4b}$$

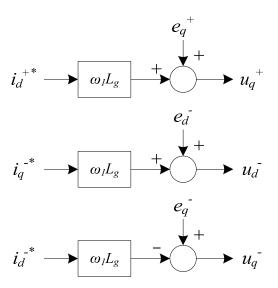

From the above equations it is straightforward to observe that each PCC voltage component is related to only one current component:  $u_q^+$  and  $i_d^+$ ;  $u_d^-$  and  $i_q^-$ ; and  $u_q^-$  and  $i_d^-$ . The current component  $i_q^+$  is related to the control of the DC-link voltage and does not influence the PCC voltage level directly. Thus, three independent voltage controllers are needed for  $u_q^+$ ,  $u_d^-$  and  $u_q^-$ . Since they are constant voltages, a Proportional-Integral (PI) controller is enough to ensure zero steady-state error. The plant models needed for the design of these controllers are shown in Figure 4 for each component, based on Equation (3b) and (4).

**Figure 4.** Plant model of the PCC voltage control for each component in dq-axes.

## 3. Control Scheme

The block diagram of the proposed control scheme is shown in Figure 5, which is composed of the following parts:

- DC-link voltage control

- Reactive power control

- PCC voltage control & calculation of  $i_q^{+*}$

- Calculation of  $i_{dq}^{+*}$  and  $i_{dq}^{-*}$

- Current control

- Modulation strategy

In first place, the active power reference  $P^*$  is set by the "DC-link voltage control" block. Its output constitutes an input for two possible blocks, namely, "Calculation of  $i_{dq}^{+*}$  and  $i_{dq}^{-*}$ " block or "PCC voltage control & calculation of  $i_q^{+*}$ " block. Depending on the application, one block or another will be chosen. The output of both blocks is the dq-axes reference current (positive and negative sequence,  $i_{dq}^{+*}$  and  $i_{dq}^{-*}$ ). The following stage is the dq to  $\alpha\beta$  transformation plus the calculation of  $i_{\alpha\beta}^*$ . Finally, the low level control is performed by the "Current control" block and the modulation strategy.

References Measurements PCC voltage control **PCC** voltage dq to  $\alpha\beta$ control DC-link & Current voltage  $\rightarrow u_{\alpha\beta}$ & control control calculation To modulator of  $i_{\alpha\beta}$ calculation of  $i_q$  $p^*$  $u_{\alpha\beta}$ Calculation Reactive  $i_{dq}^{+*}$  &  $i_{dq}$ power Q control Equation (10)

**Figure 5.** Control scheme including the PCC voltage controller.

## 3.1. DC-link Voltage Control

The DC-link voltage controller is usually based on a PI controller along with an antiwindup mechanism. However, this scheme may not be sufficient in the case of weak grids. Due to the compensation of the negative sequence voltage at the PCC, an oscillation of frequency  $2\omega_1$  appears in  $u_{DC}$ . If  $u_{DC}$  is not filtered, this oscillation propagates through the control system, appearing in  $P^*$  and, therefore, in the reference currents. The oscillation of frequency  $2\omega_1$  in dq-axes is transformed into an oscillation of frequency  $3\omega_1$  in the abc-axes.

In short, if  $u_{DC}$  is not filtered, the PCC currents will be affected by the appearance of a 3rd order harmonic (this being no zero-sequence harmonic). To eliminate this harmonic, the 2nd order oscillation is removed from the measured  $u_{DC}$  by means of a band-pass filter centered at  $\omega_0 = 2\omega_1$ . This filter is implemented with a Second Order Generalized Integrator for Quadrature Signal Generation (SOGI-QSG) [11], using the output in phase with the input since its transfer function behaves as a band-pass filter centered at  $\omega_0$ . This way, the dynamics of the mean value of the DC-link voltage is not altered.

The block diagram of the DC-link voltage controller is shown in Figure 6, where  $k_{px}$  is the proportional gain,  $k_{ix}$  is the integral gain and  $k_{awx}$  is the antiwindup gain. The DC-link model based on the energy stored in the capacitor has been used [12]. As mentioned before, the basis of the DC-link voltage control is a PI controller and its parameters are tuned without taking into account the inner current controller. To do so, the Zero-Order Hold (ZOH) method has been applied to the plant to obtain its discrete time version, where  $C_{DC} = (C_{DC1} \cdot C_{DC2})/(C_{DC1} + C_{DC2})$ :

$$G_{DC}(z) = \frac{2T_s}{C_{DC}(z-1)} \tag{5}$$

The PI controller can be expressed in pole-zero form as:

$$C(z) = k_{px} \frac{z - \alpha}{z - 1} \tag{6}$$

where  $\alpha = 1 - (k_{ix}T_s/k_{px})$ . The open-loop transfer function has two poles placed at  $z_p = 1$  and a zero placed at  $z_z = \alpha$ . Depending of the controller gain, the closed loop system  $G_{CL}(z)$  can have two conjugate poles as shown. In this case, the general form of the denominator polynomial of  $G_{CL}(z)$  is:

$$den\{G_{CL}(z)\} = \left(z - \rho e^{j\vartheta}\right)\left(z - \rho e^{-j\vartheta}\right) = z^2 - (2\rho\cos\vartheta)z + \rho^2 \tag{7}$$

where  $\rho = e^{-\xi \omega_n T_s}$ ,  $\vartheta = \omega_n T_s \sqrt{1 - \xi^2}$ ,  $\omega_n$  is the natural pulsation and  $\xi$  is the damping coefficient. To avoid a large overvoltage in  $u_{DC}$ , the damping coefficient has to be chosen as  $\xi \ge 1/\sqrt{2}$ . From settling time and damping coefficient values,  $\omega_n$  can be calculated with the expression  $t_s \approx 4.6/\xi \omega_n$  for a second order system. To verify these conditions,  $k_{px}$  and  $\alpha$  have to take the next values:

$$k_{px} = \frac{(1 - \rho \cos \theta)C_{DC}}{T_s} \tag{8}$$

$$\alpha = \frac{1 - \rho^2}{2(1 - \rho \cos \theta)} \tag{9}$$

and then  $k_{ix} = (1 - \alpha)k_{px}/T_s$ . The antiwindup gain is chosen as  $k_{awx} = 1/k_{px}$ .

## 3.2. Reactive Power Control

This is a controller associated to variables that modify the reactive power at the PCC. In this case, this block specifies the reactive power reference  $Q^*$ , which is an output to the block "Calculation of  $i_{dq}^{+*}$  &  $i_{dq}^{-*}$ ". Another variable that could be used to modify the reactive power at the PCC is the power factor.

$u_{DC}^*$   $u_{DC}$   $u_$

**Figure 6.** Block diagram of the "DC-link voltage control" of Figure 5.

# 3.3. Calculation of $i_{dq}^{+*}$ and $i_{dq}^{-*}$

This controller is regulated by the equation system in Equation (10). It relates active power, reactive power, PCC voltage and current in dq-axes and it is usually employed in active and reactive power control, as well as in power factor control. Active and reactive powers are divided into three parts: average power (P and Q), oscillating power with cosine terms [ $P_{2\omega(c)}$  and  $Q_{2\omega(c)}$ ] and oscillating power with sine terms [ $P_{2\omega(s)}$  and  $Q_{2\omega(s)}$ ]. If grid conditions are balanced, these four oscillating powers are zero and there are only positive sequence voltages and currents. Multiplying by the inverse matrix, the corresponding expressions for the calculation of the reference currents are obtained ( $i_{dq}^+$  and  $i_{dq}^-$ ). To do so,  $P_{2\omega(c)}$  and  $P_{2\omega(s)}$  are set to zero to compensate the unbalance caused by negative sequence voltage and  $Q_{2\omega(c)}$  and  $Q_{2\omega(s)}$  are not controlled, therefore their corresponding rows are eliminated from Equation (10). Trying to control these oscillating reactive powers only deteriorates the control performance, therefore they are allowed to run freely:

$$\begin{bmatrix}

P_{0} \\

P_{2\omega(c)} \\

P_{2\omega(s)} \\

Q_{0} \\

Q_{2\omega(c)} \\

Q_{2\omega(s)}

\end{bmatrix} = \begin{bmatrix}

u_{d}^{+} & u_{q}^{+} & u_{d}^{-} & u_{q}^{-} \\

u_{d}^{-} & u_{q}^{-} & u_{d}^{+} & u_{q}^{+} \\

u_{q}^{-} & -u_{d}^{-} & -u_{q}^{+} & u_{d}^{+} \\

u_{q}^{+} & -u_{d}^{+} & u_{q}^{-} & -u_{d}^{-} \\

u_{q}^{-} & -u_{d}^{-} & u_{q}^{+} & -u_{d}^{+} \\

-u_{d}^{-} & -u_{q}^{-} & u_{d}^{+} & u_{q}^{+}

\end{bmatrix} \cdot \begin{bmatrix} i_{d}^{+} \\ i_{q}^{+} \\ i_{d}^{-} \\ i_{q}^{-} \end{bmatrix} \tag{10}$$

#### 3.4. PCC Voltage Control

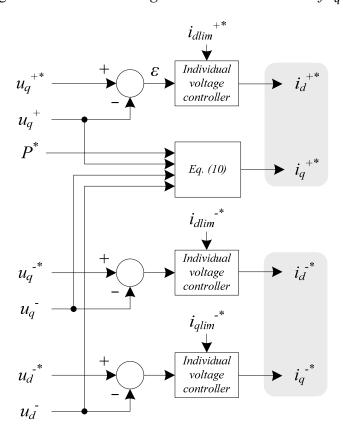

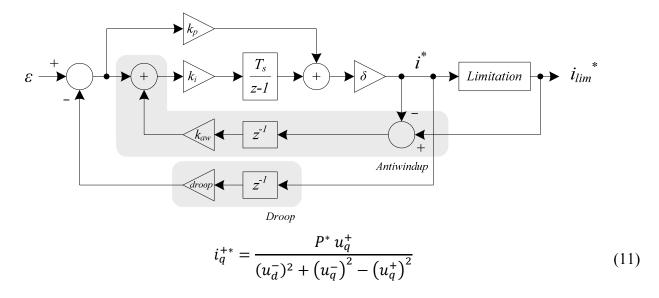

The block diagram of the PCC voltage controller is shown in Figure 7 and it is implemented in dq-axes. This stage is formed by three "individual voltage controllers" in parallel, whose outputs are  $i_d^{+*}$ ,  $i_d^{-*}$  and  $i_q^{-*}$ , plus the calculation of  $i_q^{+*}$  by means of Equation (11). This equation is obtained from Equation (10). The minus sign that goes with  $u_q^+$  is due to the current direction. These four outputs are the references for the current controller. In this figure,  $\varepsilon$  represents the error signal and the subscript "lim" stands for "limited". The reference voltages  $u_q^{-*}$  and  $u_q^{-*}$  are set to zero in order to eliminate the PCC voltage negative sequence, whereas the reference voltage  $u_q^{+*}$  should be equal to the PCC fundamental voltage.

The inner structure of each "individual voltage controller" is depicted in Figure 8. As mentioned, it is mainly formed by a PI controller with a forward Euler integrator. The constant  $\delta$  is 1 for the voltage controllers of  $u_q^+$  and  $u_d^-$ , and -1 for the voltage controller of  $u_q^-$  due to the minus sign in Equation (4b).

It is a first order system and, considering the cascaded system of Figure 5, the tuning goal is to achieve a settling time larger than ten times the settling time of the current controller  $(t_s|_{vc} > 10 \cdot t_s|_{cc})$ , where  $t_s$  is the settling time, "vc" means voltage control and "cc" means current control). This constraint affects the position of the closed-loop pole introduced by the PI controller. The integral constant  $(k_i)$  helps achieve zero steady-state error in the event of model mismatch and disturbances. Therefore, the parameter tuning is focused on settling time and controller bandwidth. The resulting parameters are  $k_p = 0.05$  and  $k_i = 350$ .

**Figure 7.** Block diagram of the "PCC voltage control & calculation of  $i_q^{+*}$ " block of Figure 5.

**Figure 8.** Block diagram of the "individual voltage controller" of Figure 7.

In order to prevent the windup of the integrator, an antiwindup mechanism has been added to each PI controller. It is characterized by the antiwindup constant, which has been set as  $k_{aw} = 0.1$ . High values for this parameter cause system instability. When using an antiwindup technique, an important detail to be taken into account is that its contribution should not be added to the integral branch of the PI controller until the whole control system starts. Otherwise, the control system would be forced to start with a non-zero error.

The linear operating range of a STATCOM with given maximum capacitive and inductive ratings can be extended if a regulation "droop" is allowed. Regulation "droop" means that the terminal voltage is allowed to be smaller than the nominal no-load value at full capacitive compensation and, conversely, it is allowed to be higher than the nominal value at full inductive compensation [13]. It also ensures automatic load sharing with other voltage compensators. Perfect regulation (zero droop or slope) could result in poorly defined operating point, and a tendency of oscillation, if the system impedance exhibited a "flat" region (low impedance) in the operating frequency range of interest [13]. It should be mentioned that this possible regulation makes sense in scenarios where there are several converters connected in parallel trying to control the PCC voltage. This droop control has been added to the voltage controller as shown in Figure 8, characterized by the constant droop = 0.01. Similarly to  $k_{aw}$ , high values for this parameter cause system instability. The expression in Equation (11) is obtained from Equation (10).

# 3.5. dq to $\alpha\beta$ Transformation and Calculation of $i_{\alpha\beta}^*$

The outputs of the first stage of the control scheme are  $i_{dq}^{+*}$  and  $i_{dq}^{-*}$ . These current references have to be transformed to  $\alpha\beta$ -axes, since the current controller is implemented in stationary reference frame. The reason for this is that a resonant controller tuned at  $\omega$  in  $\alpha\beta$ -axes is able to compensate both positive and negative sequences, whereas in dq-axes two controllers would be necessary, a PI controller and a resonant controller tuned at  $2\omega_1$ . The fact of increasing the number of controllers connected in parallel endangers the system stability and increases the settling time of the controller.

Positive and negative sequence current references in  $\alpha\beta$ -axes are calculated as shown in Equation (12a) and (12b). The estimated phase angle  $\hat{\theta}$  of the positive sequence voltage vector is obtained with a PLL, whose bandwidth is 20 Hz. This results in a good tradeoff between selectivity, steady-state error and response speed. Afterwards, the final current references are calculated according to Equation (13a) and (13b):

$$\begin{bmatrix} i_{\alpha}^{+*} \\ i_{\beta}^{+*} \end{bmatrix} = \begin{bmatrix} \cos \hat{\theta} & -\sin \hat{\theta} \\ \sin \hat{\theta} & \cos \hat{\theta} \end{bmatrix} \cdot \begin{bmatrix} i_{d}^{+*} \\ i_{q}^{+*} \end{bmatrix}$$

(12a)

$$\begin{bmatrix} i_{\alpha}^{-*} \\ i_{\beta}^{-*} \end{bmatrix} = \begin{bmatrix} \cos \hat{\theta} & \sin \hat{\theta} \\ -\sin \hat{\theta} & \cos \hat{\theta} \end{bmatrix} \cdot \begin{bmatrix} i_{d}^{-*} \\ i_{q}^{-*} \end{bmatrix}$$

(12b)

$$i_{\alpha}^{*} = i_{\alpha}^{+*} + i_{\alpha}^{-*} \tag{13a}$$

$$i_{\beta}^* = i_{\beta}^{+*} + i_{\beta}^{-*}$$

(13b)

# 3.6. Current Controller

The third stage of the control scheme is the current controller. The harmonics present in power systems are those of order  $6k \pm 1$  ( $k \in \mathbb{Z}$ ), which turn into 6k ( $k \in \mathbb{Z}$ ) when changing the reference

frame from stationary (abc or  $\alpha\beta$ ) to synchronous (dq). This allows halving the number of resonant controllers needed to implement the current controller [14]. Therefore, since the 5th (negative sequence) and 7th (positive sequence) harmonics are usually present in the grid, the current control scheme of Figure 9 has been used to obtain the simulation results. It consists of two resonant controllers (SOGIs) tuned at  $\omega_1$  and  $6\omega_1$  (the blocks labeled as " $\omega_1$ " and " $6\omega_1$ " are composed of an integral gain  $k_i$  connected in series with a SOGI), a feedforward of the positive sequence PCC voltage, and  $\alpha\beta$  to dq and dq to  $\alpha\beta$  transformations. A feedforward of the total PCC voltage (including negative sequence) would introduce non-desired harmonics in the control. The error signals in  $\alpha\beta$ -axes and dq-axes are  $\varepsilon_{\alpha\beta}$  and  $\varepsilon_{dq}$ , respectively.

$i_{\alpha\beta}^{*}$   $i_{\alpha\beta}$   $i_{\alpha\beta}$

Figure 9. Block diagram of the block "Current control" of Figure 5.

In general, the resonant frequency of the SOGI is represented by  $\omega_0$ . The discrete SOGI transfer function is given by Equation (14) and, if  $\omega_0^2 T_s^2 \ll 2$ , which is verified for  $T_s \ll 1.4$  ms (supposing that  $\omega_0^2 T_s^2 = 0.2$  is small enough, *i.e.*, a factor of 10) and if  $\omega_0 = 2\pi 50$  rad/s, Equation (14) can be approximated by Equation (15):

$$G_{SOGI}(z) = \frac{\omega_0 T_s z(z-1)}{(z-1)^2 + \omega_0^2 T_s^2 z}$$

(14)

$$G_{SOGI}(z) \approx \frac{\omega_0 T_s z}{z - 1}$$

(15)

The SOGI is combined with a proportional and integral gain ( $k_p$  and  $k_i$ , respectively) to form the current controller. The resulting transfer function can be expressed as:

$$G_{P+SOGI}(z) = k_p + k_i \frac{\omega_0 T_s z}{z - 1} = K_p \frac{z - \alpha}{z - 1}$$

(16)

where  $K_p = k_p + k_i \omega_0 T_s$  and  $\alpha = \frac{k_p}{k_p + k_i \omega_0 T_s}$ . It is important to notice that the approximation made for Equation (15), *i.e.*, if  $\omega_0^2 T_s^2 \ll 2$ , will not be valid for every frequency and for every sampling period. The current controller parameters take the following values:

$$K_p = \frac{1 + a - 2\rho\cos\theta}{h} \tag{17a}$$

$$\alpha = \frac{a - \rho^2}{bK_p} \tag{17b}$$

where  $\rho = e^{-\xi \omega_n T_s}$ ,  $\vartheta = \omega_n T_s$ ,  $\omega_n$  is the natural pulsation,  $\xi$  is the damping factor,  $a = e^{-\frac{RT_s}{L}}$  and b = (1-a)/R. Then,  $k_p = \alpha K_p$  and  $k_i = (K_p - k_p)/\omega_0 T_s$ .

To help decreasing the computational burden, the trigonometric functions employed in the calculation of these transformations can be implemented by means of look-up tables if the digital platform has enough memory.

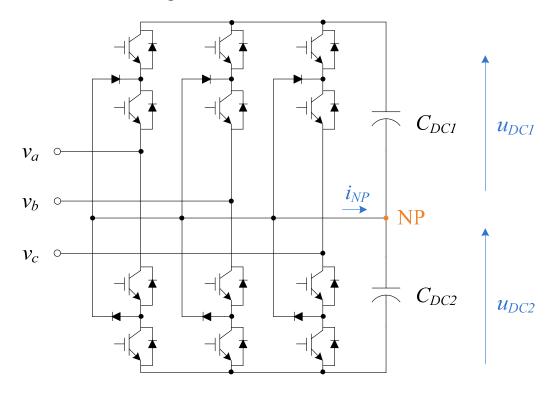

# 3.7. Modulation Strategy

The NPC converter, whose scheme is shown in Figure 10, has some drawbacks such as the additional clamping diodes, a more complicated PWM switching pattern design and possible deviation of neutral point (NP) voltage [15]. The capacitors can be charged or discharged by neutral current  $i_{NP}$ , causing NP voltage deviation. It might appear a ripple of frequency three times the fundamental in  $u_{DC1}$  and  $u_{DC2}$  that can destroy components if both DC-link voltages are not balanced.

To minimize this effect, a carrier-based PWM strategy with zero-sequence voltage injection [16] is applied to the three-level NPC converter. Using this technique, the locally averaged NP current is kept to zero, and consequently, the locally averaged voltages on the DC-link capacitors are constant [17].

#### 4. Online Adaptation of the DC-Link Reference Voltage

To enable the power transfer between the grid and the DC-link capacitors,  $u_{DC}$  must be greater than  $\sqrt{2} v_{LL}$ , where  $v_{LL}$  is the RMS phase-to-phase NPC output voltage. When calculating the reference DC-link voltage, a safety margin  $\Delta u_{DC}$  is usually given to ensure the energy transfer in case of voltage fluctuations. This margin takes values from 20 V to 50 V in weak grids. Therefore, the calculation of  $u_{DC}^*$  is shown in Equation (18):

$$u_{DC}^* \ge \sqrt{2} \, v_{LL} + \Delta u_{DC} \tag{18}$$

When the PCC voltage is expected to suffer large variations, as in the case of weak grids,  $u_{DC}^*$  should be recalculated online to adapt its value to the actual AC voltage. In this way, the modulation index is kept around its optimal value, *i.e.*,  $m_a \approx 1$ . Otherwise, the modulation index will be altered, which can increase the converter power losses, modify the expected harmonic content and worsen the overall system performance [15]. It is also advisable to limit the possible values of  $u_{DC}^*$  so that controllability is always ensured, as in the case of voltage dips, and limit the transition rate of  $u_{DC}^*$ .

Figure 10. Three-level NPC converter.

# 5. Sampling Mode When Working With an L-Filter

One of the essential parts of the converter control is the synchronization system, which allows detecting the angle of the PCC voltage vector. This angle would coincide with that of the grid voltage if it were an ideal grid. Generally, the grid impedance is neglected in terms of controller design, considering the voltage at the PCC as the system voltage [18].

Blasko *et al.* [19] established that the optimal moment to sample the currents are those in which the PWM carrier signal reaches its maximum and minimum value, since it is in those moments when the zero-crossing of the current ripple takes place. When working with an LCL-filter and a non-ideal grid, and sampling the PCC voltage at those same moments, the obtained PCC voltage in *dq*-axes corresponds to its actual value. However, this is not the same situation when working with an L-filter and a non-ideal grid. In this case, the PCC voltage presents a ripple in which two envelopes can be seen. By sampling synchronously with the sampling period of the currents, which is also the controller sampling period, the obtained PCC voltage corresponds to one of those envelopes, giving rise to incorrect projections of the PCC voltage on the *dq*-axes.

Briz *et al.* [20] posed two alternative methods to the method suggested by Blasko for sampling the currents, when the inverter is connected to a load whose natural frequency may be close to the sampling frequency. In such cases, the method based on the maximum and minimum points of the carrier signal introduces an error at the current fundamental frequency as well as aliasing problems. The methods the authors proposed were based on advancing the sampling instant and on multi-sampling per switching period.

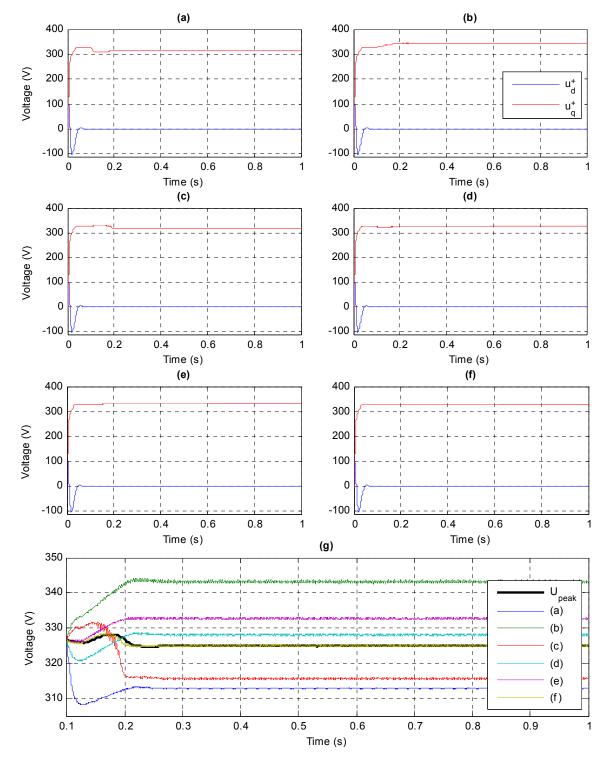

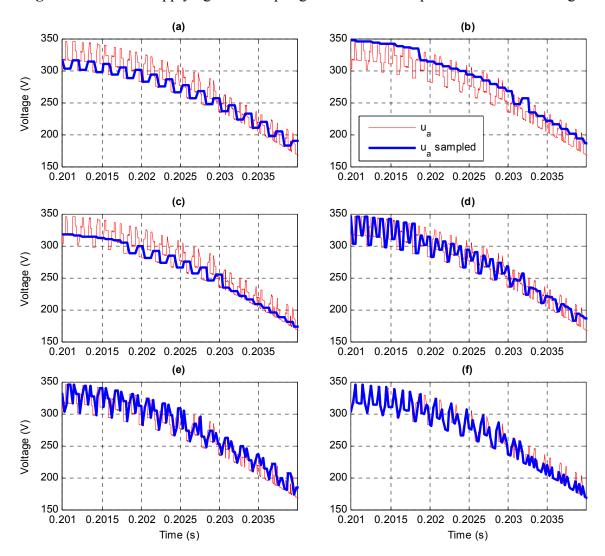

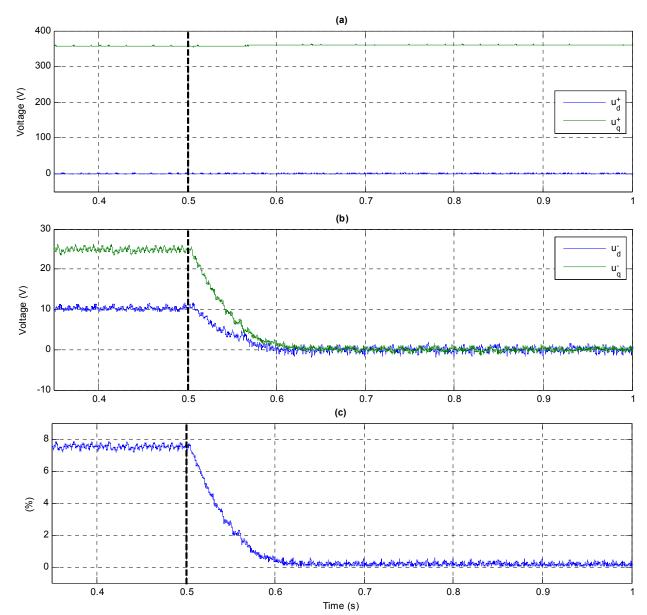

The methods studied here for sampling the PCC voltage are similar to those shown in [20]. With the system configuration defined in Table 1, several methods for performing the PCC voltage sampling are shown in Figure 11 [21]:

(a) The previously mentioned sampling method synchronized with the current sampling, where the sampling period of the PCC voltage and the timer,  $T_{ss}$ , is equal to  $T_s$  (Figure 12a);

- (b) Sampling at the midpoint of  $T_s$ , with  $T_{ss} = T_s$ , which obtains a PCC voltage in dq-axes higher than the real value (Figure 12b);

- (c) Sampling shifted a time  $t_{ad}$  with respect to the sampling instants of the current, where  $T_{ss} = T_s$  and where the voltage remains erroneous (Figure 12c, where  $t_{ad} = T_s/4$ );

- (d) Oversampling of two samples, synchronized with  $T_s$ , where  $T_{ss} = T_s/2$  and for which the voltage remains slightly erroneous (Figure 12d);

- (e) Oversampling of three samples, synchronized with  $T_s$ , where  $T_{ss} = T_s/3$  and for which the voltage still remains slightly erroneous (Figure 12e), and

- (f) Oversampling of four samples, which obtains a correct PCC voltage in dq-axes (Figure 12f).

| Parameter                 | Symbol     | Value           | Units |

|---------------------------|------------|-----------------|-------|

| Base apparent power       | $S_{base}$ | 100             | kVA   |

| Base voltage              | $U_n$      | $400\sqrt{2/3}$ | V     |

| Fundamental pulsation     | $\omega_1$ | $2\pi50$        | rad/s |

| Grid-filter inductance    | L          | 0.2209          | p.u.  |

| Grid-filter resistance    | R          | 0.0034          | p.u.  |

| Grid-impedance inductance | $L_{g}$    | 0.0736          | p.u.  |

| Grid-impedance resistance | $R_g$      | 0.0005          | p.u.  |

| Switching period          | $T_{sw}$   | 200             | μs    |

| Sampling period           | $T_s$      | 100             | μs    |

**Table 1.** System parameters with L-filter and non-ideal grid.

**Figure 11.** Methods for performing the PCC voltage sampling [21].

**Figure 12.** Estimated  $u_{dq}^+$  ( $\tilde{u}_q^+$ ) with (a) sampling synchronized; (b) sampling at the midpoint; (c) sampling shifted; (d) oversampling of two samples; (e) oversampling of three samples; and (f) oversampling of four samples; (g) Comparison of the  $u_q^+$  obtained with the six methods after the initial transient with respect to the peak value of the fundamental PCC phase voltage  $(U_{peak})$ .

The estimated  $u_q^+$  ( $\tilde{u}_q^+$ ) in steady-state with the six methods mentioned above are compared with the peak value of the fundamental PCC voltage in Figure 12g. Figure 13 shows the effect of applying

each sampling method on the *a*-phase of the PCC voltage. It is straightforward to see the relationship between Figures 12g and 13:

- Methods (a) and (c) detect an inner envelope of u, giving  $\tilde{u}_q^+ < u_q^+$ . Besides, the envelope detected with method (c) is the one closest to the fundamental voltage and, thus,  $\tilde{u}_q^+|_{a)} < \tilde{u}_q^+|_{c)} < u_q^+$ ;

- Method (b) detects an outer envelope of u, yielding  $\tilde{u}_q^+|_{b} > u_q^+$ ;

- Methods (d) and (e) perform a more precise detection of the PCC voltage than methods (a) to (c), although there is still a small steady-state error. It is also observed that  $\tilde{u}_q^+|_{e)} > \tilde{u}_q^+|_{d)} > u_q^+$  in spite of using a higher oversampling, which is due to the sampling at highly-noisy points of u;

- Method (f), *i.e.*, oversampling of four samples synchronized with  $T_s$ , is the only method that performs a precise detection of the PCC fundamental voltage:  $\tilde{u}_q^+|_{f} \approx u_q^+$ .

The initial transient in the estimation of  $u_{dq}^+$  (Figure 12a–f) is due to the stabilization process of the PLL. However, this transient is not significant from the viewpoint of control performance because the converter control system only starts when the PLL is stable.

**Figure 13.** Effect of applying each sampling method on the *a*-phase of the PCC voltage.

#### 6. Simulation Results

#### 6.1. Weak Grid Without Harmonics

A simulation has been carried out with MATLAB/Simulink<sup>®</sup> in order to test the performance of the proposed voltage controller. The ideal grid voltage of Figure 2 has been considered, along with the system parameters of Table 1. The NPC rated power is 100 kVA and the DC-link capacitors have a value of  $C_{DC1} = C_{DC2} = 4.5$  mF. No load is connected to the PCC. The proposed voltage controller is enabled at t = 0.5 s.

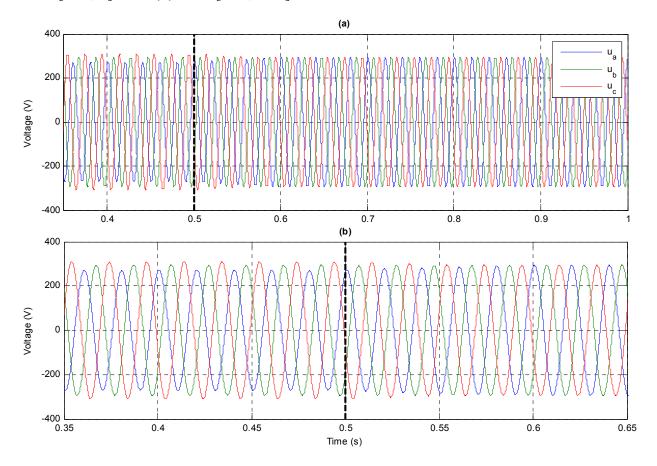

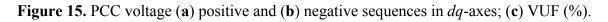

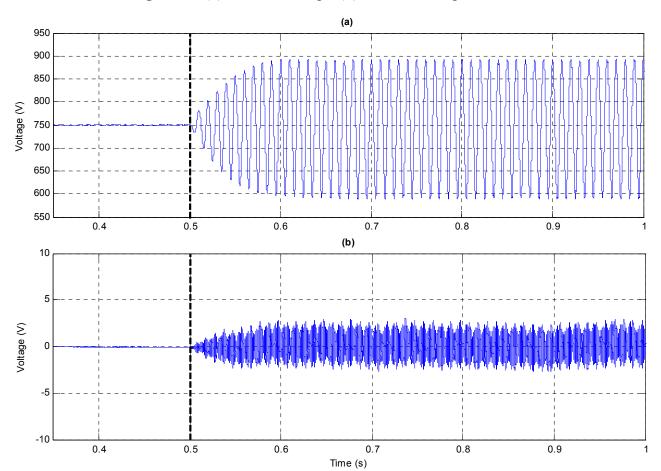

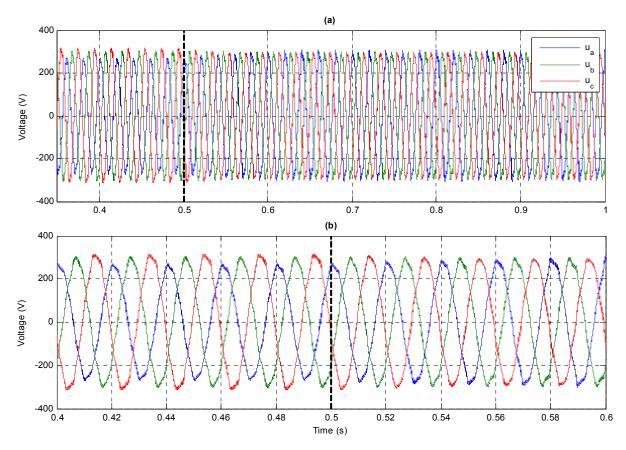

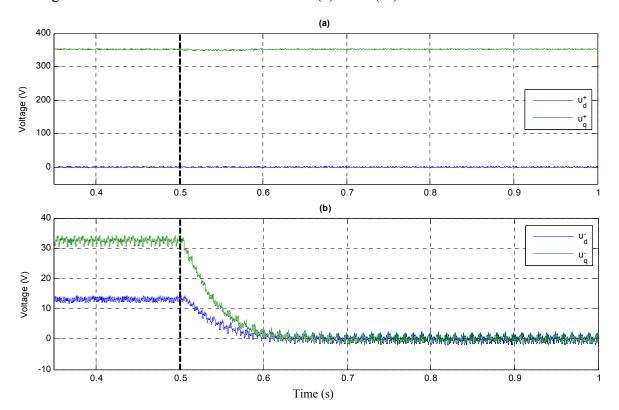

Figure 14 shows the temporary evolution of the filtered PCC voltage in abc-axes. Its non-filtered waveform presents a high ripple due to the high grid impedance and, in order to appreciate the effect of the PCC voltage controller, its filtered waveform is the one represented. In the following figures, the corresponding control activation time is marked with a dashed black line. It is clear that, when the voltage control is enabled, the PCC voltage is balanced. This is corroborated by decomposing this voltage in their positive and negative sequences as shown in Figure 15. The positive sequence  $u_{dq}^+$  remains equal because its reference voltage corresponds to the value it had before enabling the PCC voltage control. The negative sequence  $u_{dq}^-$  becomes almost zero since its reference voltage is set to zero for both d and q components, as well as the VUF.

**Figure 14.** Filtered PCC voltage in *abc*-axes. (a) Representation of the waveforms in t = [0.35, 1] s and (b) in t = [0.35, 0.65] s.

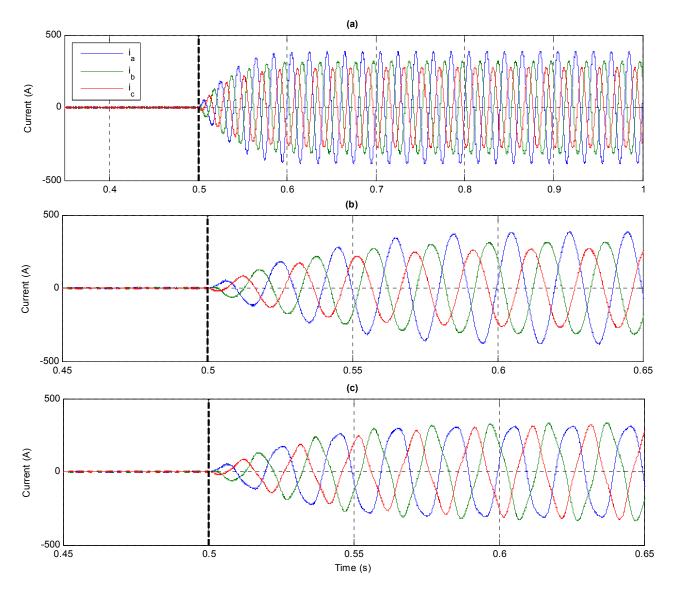

The current flowing from the VSC to the grid is represented in Figure 16a in *abc*-axes. Since no load is connected to the PCC, the current before enabling the voltage control is zero. Afterwards, the VSC provides an unbalanced current in order to compensate the negative sequence component. This is better observed in Figure 16b, which is a representation of Figure 16a between  $t = [0.45 \ 0.65]$  s. Figure 16c is the equivalent of Figure 16b if the resonant controller  $2\omega$  is not included in the DC-link voltage controller, showing a PCC current with a 3rd order harmonic.

**Figure 16.** (a) PCC current in *abc*-axes; (b) Zoom of (a) between t = [0.45, 0.65] s; (c) Equivalence to (b) if the band-pass filter in the DC-link voltage controller is not included.

Since the PCC voltage is no longer unbalanced due to the effect of the voltage controller, the unbalance now appears in  $u_{DC}$ . Figure 17a shows that a large oscillation appears in  $u_{DC}$ , reaching nearly  $\pm 150$  V. Besides, the DC-link voltage unbalance, calculated as the difference between positive and negative DC-link voltages ( $u_{DC1} - u_{DC2}$ ), also increases. If the oscillation level is not permissible, the reference for the negative sequence voltage can be set with a value different from zero but still low enough to satisfy regulations when it comes to maximum PCC voltage unbalance. In any case, it is worth remembering that the high level of unbalance applied to carry out these tests is usually not found in a real power system, so that in practice the amplitude of the oscillation will be much smaller. According to current regulations, a VUF greater than 2% in the worst case (e.g., IEC 61000-3-13 regulation) and 3% in the best case (e.g., ENTSO-E regulation) requires the disconnection of the converter from the grid, which can be avoided with the proposed PCC voltage controller.

Figure 17. (a) DC-link voltage; (b) DC-link voltage unbalance.

# 6.2. Weak Grid With 5th and 7th Order Harmonics and a Higher Level of Negative Sequence

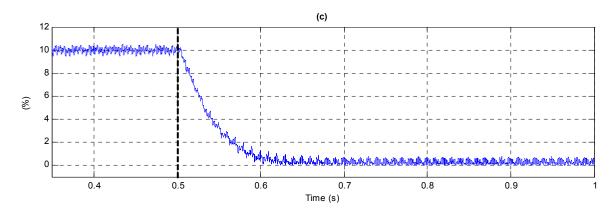

In order to test the performance of the proposed PCC voltage controller in a more realistic situation, 5th and 7th order harmonics have been included in the grid voltage with a level of  $A_5 = 0.01 \cdot A_1$  and  $A_7 = 0.03 \cdot A_1$ , respectively. Furthermore, a higher level of negative sequence has been chosen (VUF = 10%). Figure 18 shows the temporal evolution of the PCC voltage waveform, validating as well the proper operation of the PCC voltage controller by compensating its negative sequence. The performance of the proposed controller is also observed in Figure 19, which collects the evolution of  $u_{dq}^+$  (Figure 19a),  $u_{dq}^-$  (Figure 19b) and the VUF (Figure 19c).

**Figure 18.** Filtered PCC voltage in *abc*-axes with 5th and 7th order harmonics. (a) Representation of the waveforms in t = [0.35, 1] s; and (b) in t = [0.35, 0.65] s.

**Figure 19.** PCC voltage (a) positive and (b) negative sequences in *dq*-axes when the grid voltage contains 5th and 7th order harmonics. (c) VUF (%).

Figure 19. Cont.

#### 7. Conclusions

This article has proposed a PCC voltage controller in synchronous reference frame to compensate an unbalanced PCC voltage by means of a STATCOM, allowing an independent control of both positive and negative voltage sequences. To do so, the grid model has been studied under unbalanced conditions, showing the equations that relate voltage and current.

This voltage controller has been placed inside a control scheme to evaluate its performance by means of simulation results. These results have demonstrated the efficacy of this controller, managing to significantly reduce the oscillation present in the DC-link voltage.

However, due to the compensation of the PCC voltage negative sequence, an oscillation appears on the DC-link voltage, with frequency twice the fundamental grid frequency. The magnitude of this oscillation depends on the level of negative sequence. If the level of this oscillation is not permissible, the voltage reference for negative sequence voltage can be set with a value different from zero but still low enough to satisfy regulations when it comes to maximum PCC voltage unbalance. This would result in a reduction of  $u_{DC}$  oscillation and DC-link voltage unbalance.

Experimental results have not been provided because the grid at our laboratory is not a weak grid and, even though this could be simulated by increasing the inductance in series with the VSC (thus, increasing the grid impedance), our three-level NPC converter has not been sized for compensating such unbalances.

#### Acknowledgments

This work has been funded by the Spanish Ministry of Economy and Competitiveness; projects ENE2011-28527-C04-01 and ENE2011-28527-C04-02.

## **Conflicts of Interest**

The authors declare no conflict of interest.

#### References

1. Piwko, R.; Miller, N.; Sánchez-Gasca, J.; Yuan, X.; Dai, R.; Lyons, J. Integrating Large Wind Farms into Weak Power Grids with Long Transmission Lines. In Proceedings of Transmission and Distribution Conference and Exhibition: Asia and Pacific, 2005 IEEE/PES, Dalian, China, 2005; pp. 1–7.

- 2. Ledesma, P.; Usaola, J.; Rodríguez, J.L. Transient stability of a fixed speed wind farm. *Renew. Energy* **2003**, *28*, 1341–1355.

- 3. Farias, M.F.; Battaiotto, P.E.; Cendoya, M.G. Wind Farm to Weak-Grid Connection Using UPQC Custom Power Device. In Proceedings of the IEEE International Conference on Industrial Technology (ICIT'10), Vi a del Mar, Chile, 14–17 March 2010; pp. 1745–1750.

- 4. Yazdani, A.; Iravani, R. *Voltage-Sourced Converters in Power Systems: Modeling, Control, and Applications*; Wiley: Hoboken, NJ, USA, 2010.

- 5. Schauder, C.; Gernhardt, M.; Stacey, E.; Lemak, T.; Gyugyi, L.; Cease, T.W.; Edris, A. Operation of ±100 MVAr TVA STATCON. *IEEE Trans. Power Deliv.* **1997**, *12*, 1805–1811.

- 6. Bollen, M.H.J. *Understanding Power Quality Problems—Voltage Sags and Interruptions*; Wiley IEEE Press: New York, NY, USA, 2000.

- 7. Pillay, P.; Manyage, M. Definitions of voltage unbalance. *IEEE Power Eng. Rev.* **2001**, *22*, 50–51.

- 8. Akagi, H.; Watanabe, E.H.; Aredes, M. *Instantaneous Power Theory and Applications to Power Conditioning*; Wiley-IEEE Press: Hoboken, NJ, USA, 2007.

- 9. Lee, C. Effects of unbalanced voltage on the operation performance of a three-phase induction motor. *IEEE Trans. Energy Convers.* **1999**, *14*, 202–208.

- 10. Kang, J.; Sul, S. Control of Unbalanced Voltage PWM Converter Using Instantaneous Ripple Power Feedback. In Proceedings of the 28th Annual IEEE Power Electronics Specialists Conference (PESC'97), St. Louis, MO, USA, 22–27 June 1997; pp. 503–508.

- 11. Rodríguez, P.; Teodorescu, R.; Candela, I.; Timbus, A.V.; Liserre, M.; Blaabjerg, F. New Positive-Sequence Voltage Detector for Grid Synchronization of Power Converters under Faulty Grid Conditions. In Proceedings of the 37th Annual IEEE Power Electronics Specialists Conference (PESC'06), Jeju, Korea, 18–22 June 2006; pp. 1–7.

- 12. Ottersten, R. On Control of Back-to-Back Converters and Sensorless Induction Machine Drives. Ph.D. Thesis, Chalmers University of Technology, Goteborg, Sweden, 2003.

- 13. Hingorani, N.G.; Gyugui, L. *Understanding FACTS: Concepts and Technology of Flexible AC Transmission Systems*; Wiley-IEEE Press: Hoboken, NJ, USA, 2000.

- 14. Bojoi, R.I.; Griva, G.; Bostan, V.; Guerriero, M.; Farina, F.; Profumo, F. Current control strategy for power conditioners using sinusoidal signal integrators in synchronous reference frame. *IEEE Trans. Power Electron.* **2005**, *20*, 1402–1412.

- 15. Wu, B. High-Power Converters and AC Drives; Wiley-IEEE Press: Hoboken, NJ, USA, 2006.

- 16. Pou, J.; Zaragoza, J.; Ceballos, S.; Saeedifard, M.; Boroyevich, D. A carrier-based PWM strategy with zero-sequence voltage injection for a three-level Neutral-Point-Clamped converter. *IEEE Trans. Power Electron.* **2012**, *27*, 642–651.

17. Pou, J.; Zaragoza, J.; Rodriguez, P.; Ceballos, S.; Sala, V.M.; Burgos, R.P.; Boroyevich, D. Fast-processing modulation strategy for the Neutral-Point-Clamped converter with total elimination of low-frequency voltage oscillations in the neutral point. *IEEE Trans. Ind. Electron.* **2007**, *54*, 2288–2294.

- 18. Cóbreces, S. Optimization and Analysis of the Current Control Loop of VSCs Connected to Uncertain Grids through LCL Filters. Ph.D. Thesis, University of Alcala, Madrid, Spain, March 2009.

- 19. Blasko, V.; Kaura, V.; Niewiadomski, W. Sampling of discontinuous voltage and current signals in electrical drives: A system approach. *IEEE Trans. Ind. Appl.* **1998**, *34*, 1123–1130.

- Briz, F.; Díaz-Reigosa, D.; Degner, M.W.; García, P.; Guerrero, J.M. Current Sampling and Measurement in PWM Operated AC Drives and Power Converters. In Proceedings of the 2010 International Power Electronics Conference (IPEC'10), Sapporo, Japan, 21–24 June 2010; pp. 2753–2760.

- 21. Huerta, F.; Cóbreces, S.; Rodríguez, F.J.; Bueno, E.; Díaz, M.J. Estudio de la Estabilidad del Modelo Discreto de Rectificadores PWM en Función de la Discretización y el Muestreo. In Proceedings of the Seminario Anual de Automática, Electrónica Industrial e Instrumentación (SAAEI'10), Bilbao, Spain, 7–9 July 2010; pp. 296–301. (in Spanish)

- © 2014 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).